LED(Light-emittingdiode)由于寿命长、能耗低等优点被广泛地应用于指示、显示等领域。可靠性、稳定性及高出光率是LED取代现有照明光源必须考虑的因素。封装工艺是影响LED功能作用的主要因素之一,封装工艺关键工序有装架、压焊、封装。由于封装工艺本身的原因,导致LED封装过程中存在诸多缺陷(如重复焊接、芯片电极氧化等),统计数据显示[1-2]:焊接系统的失效占整个半导体失效模式的比例是25%~30%,在国内[3],由于受到设备和产量的双重限制,多数

生产厂家采用人工焊接的

方法,焊接系统不合格占不合格总数的40%以上。

ZM�`6z�S�! z}&?^YU*)` 从使用角度

分析,LED封装过程中产生的缺陷,虽然使用初期并不影响其光电性能,但在以后的使用过程中会逐渐暴露出来并导致器件失效。在LED的某些应用领域,如高精密航天器材,其潜在的缺陷比那些立即出现致命性失效的缺陷危害更大。因此,如何在封装过程中实现对LED芯片的

检测、阻断存在缺陷的LED进入后序封装工序,从而降低生产成本、提高

产品的

质量、避免使用存在缺陷的LED造成重大损失就成为LED封装行业急需解决的难题。

QX1QYwcm�G xT�6&�;,|` 目前,LED产业的检测

技术主要集中于封装前晶片级的检测[4-5]及封装完成后的成品级检测[6-7],而国内针对封装过程中LED的检测技术尚不成熟。本文在LED芯片非接触

检测方法的基础上[8-9],在LED引脚式封装过程中,利用p-n结光生伏特效应,分析了封装缺陷对光照射LED芯片在引线支架中产生的回路光电流的影响,采用电磁感应定律测量该回路光电流,实现LED封装过程中芯片质量及封装缺陷的检测。

W�wG78b-OA �FAkjFgUJp 1理论分析 BQu�_�)��@ xOn��b�Y�U 1.1p-n结的光生伏特效应[m]根据p-n结光生伏特效应,光生电流IL表示为:

WDQtj�$e+ 91d�@�/�z  g S� x�K9P

g S� x�K9P 式中,A为p-n结面积,q是

电子电量,Ln、Lp分别为电子和空穴的扩散长度,J表示以光子数计算的平均光强,α为p-n结

材料的吸收系数,β是量子产额,即每吸收一个光子产生的电子一空穴对数。

[-��C�-+jC 9 f�$S4O�5 在

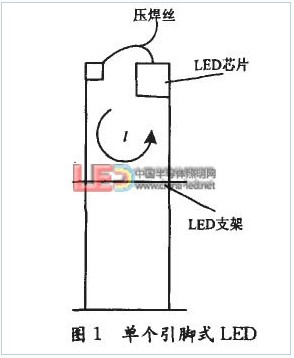

LED引脚式封装过程中,每个LED芯片是被固定在引线支架上的,LED芯片通过压焊金丝(铝丝)与引线支架形成了闭合回路,如图1。若忽略引线支架电阻,LED支架回路光电流等于芯片光生电流IL。可见,当p-n结材料和掺杂浓度一定时,支架回路光电流与光照强度I成正比。

G%�0G$3�W" (}E-+:vF�U  e��Bi

�P\� 1.2封装缺陷机理 4��

4%jz-m h�C�R�W0

I

e��Bi

�P\� 1.2封装缺陷机理 4��

4%jz-m h�C�R�W0

I LED芯片受到腐蚀因素影响或沾染油污时,在芯片电极表面生成一层非金属膜,产生封装缺陷[11]。电极表面存在非金属膜层的LED芯片压焊工序后,焊接处形成金属一介质-金属结构,也称为隧道结。当一定强度的光照射在LED芯片上,若LED芯片失效,支架回路无光电流流过若非金属膜层足够厚,只有极少数电子可以隧穿膜层势垒,LED支架回路也无光电流流过;若非金属膜层较薄,由于LED芯片光生电流在隧道结两侧形成电场,电子主要以场致发射的方式隧穿膜层,流过单位面积膜层的电流可表示为。

�,])@?TJb@ ),

�`MAevp  rh�Fa rm4a

rh�Fa rm4a 其中q为电子电量,m为电子质量,矗为普朗克常数,vx、vy、vz分别是电子在x、y、z方向的隧穿速度,T(x)为电子的隧穿概率。又任意势垒的电子隧穿概率可表示为

M�i'���Q5m  �aM'0O X�?$E�b���

X�?$E�b��� x指向为芯片电极表面到压焊点,为膜层中z方向任意点的势垒,E是垂直芯片电极表面速度为vx电子的能量。

yAEOn/.��~  ]� d| -r:4

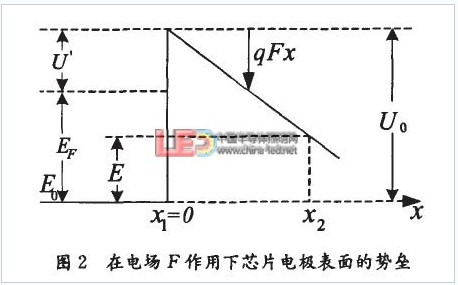

]� d| -r:4 图2为在电场f’作用‘F芯片电极表面的势垒图,其中EF为费米能级,U''为电子发射势垒。由图2,若芯片电极表面为突变结,其值为U0,光生电流在隧道结两侧形成的电场强度为F,电极表面以外的势垒为U0-qFx。取芯片电极导带底为参考能级E0(x=0),因而有x